| Today                                                                                                                                                               |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| <ul> <li>Problems <ul> <li>memory size</li> <li>multitasking</li> </ul> </li> <li>Different from caching?</li> <li>TLB</li> <li>co-existing with caching</li> </ul> |   |

| Caltech CS184b Winter2001 DeHon                                                                                                                                     | 2 |

### Problem 1:

- Real memory is finite

- Problems we want to run are bigger than the real memory we may be able to afford...

- larger set of instructions / potential operations

- larger set of data

- Given a solution that runs on a big machine

- would like to have it run on smaller machines, too

3

• but maybe slower / less efficiently

Caltech CS184b Winter2001 -- DeHon

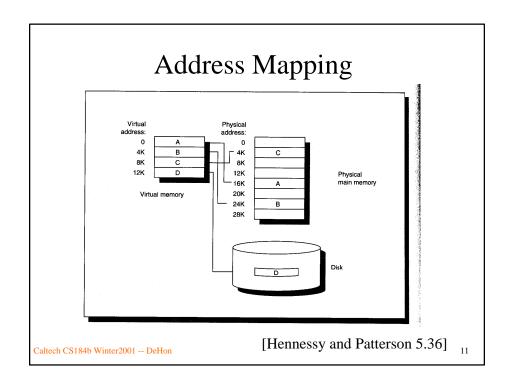

## One Solution

- Support large address space

- Use cheaper/larger media to hold complete data

- Manage physical memory "like a cache"

- Translate large address space to smaller physical memory

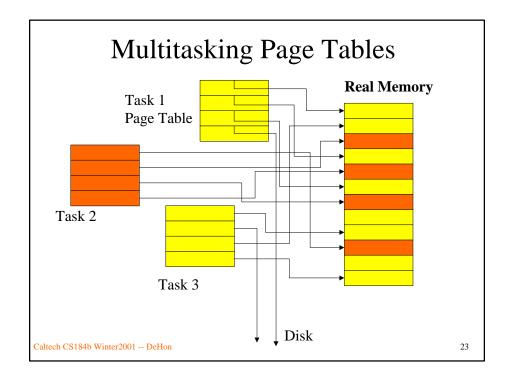

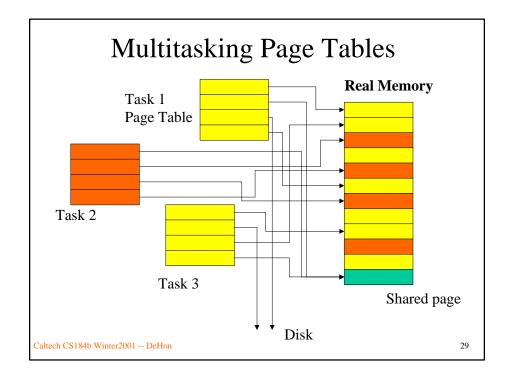

- Once do translation

- translate multiple address spaces onto real memory

7

Caltech CS184b Willse transfation to define/limit what can touch

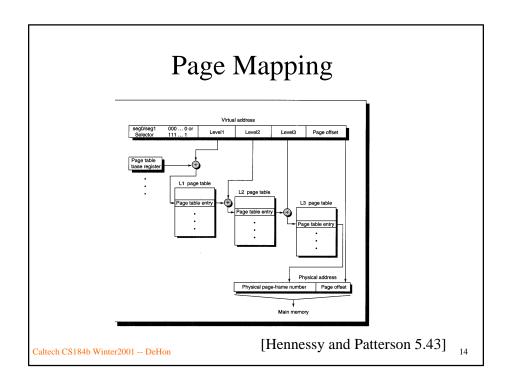

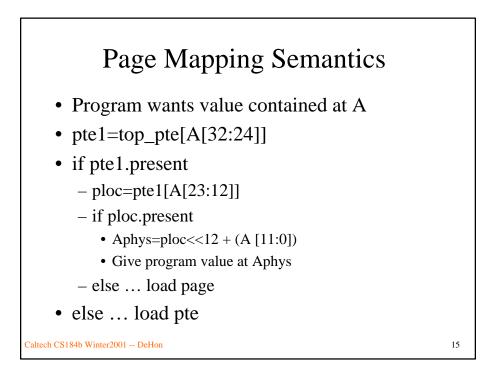

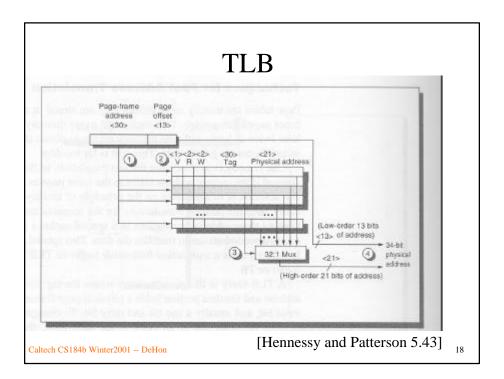

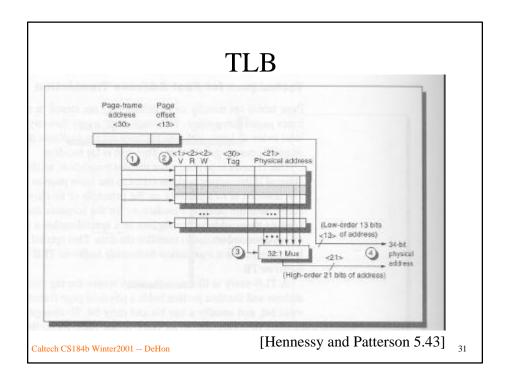

#### Modern Machines

- Keep hierarchical page table

- Optimize with lightweight hardware assist

- Translation Lookaside Buffer (TLB)

- Small associative memory

- maps physical address to virtual

- in series/parallel with every access

- faults to software on miss

- software uses page tables to service fault

17

Caltech CS184b Winter2001 -- DeHon

#### VM Page Replacement

- Like cache capacity problem

- Much more expensive to evict wrong thing

- Tend to use LRU replacement

- touched bit on pages (cheap in TLB)

- periodically (TLB miss? Timer interrupt) use to update touched epoch

19

- Writeback (not write through)

- Dirty bit on pages, so don't have to write back unchanged page (also in TLB)

Caltech CS184b Winter2001 -- DeHon

# Physically Mapped Cache

- Must translate address before can check tags

- TLB translation can occur in parallel with cache read

- (if direct mapped part is within page offset)

- contender for critical path?

- No need to flush between tasks

- Shared code/data not require flush/reload between tasks

35

• Caches big enough, keep state in cache Caltech CSI8between tasks