# CS184b: Computer Architecture [Single Threaded Architecture: abstractions, quantification, and optimizations]

Day13: February 20, 2000 Cache and Memory System Optimization

# Today

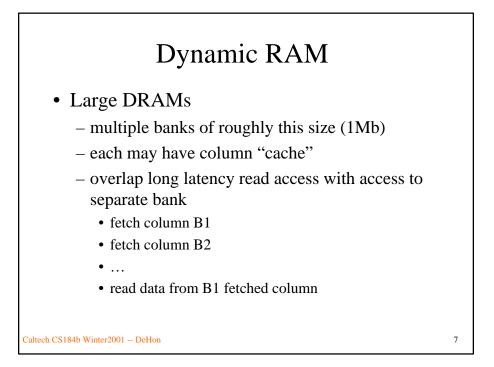

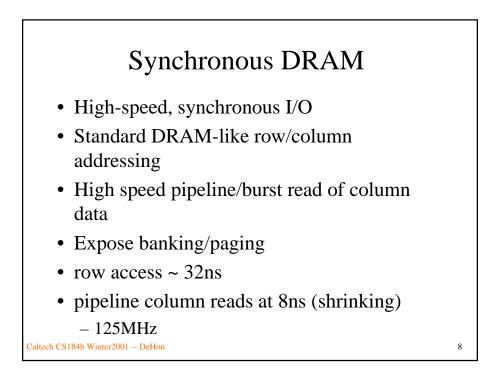

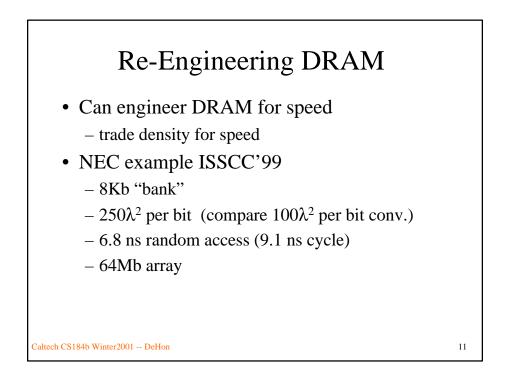

- DRAM (Main Memory) technology

- Spatial Locality

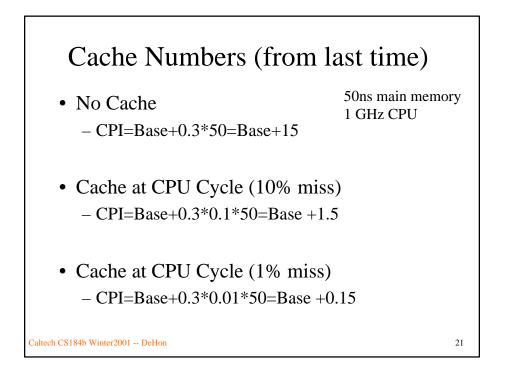

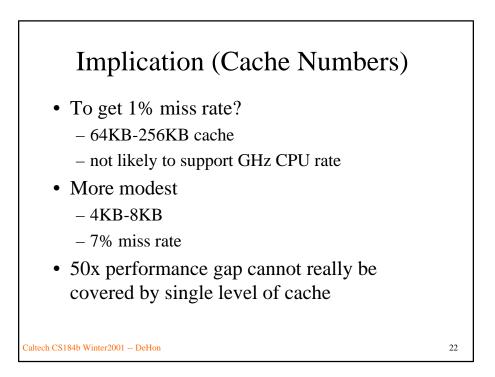

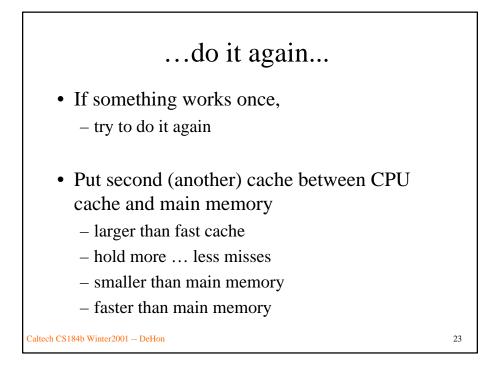

- Worked once, do it again...

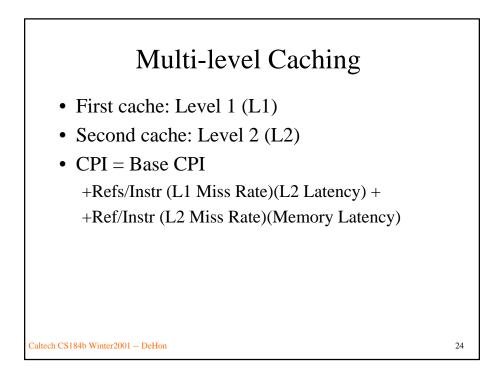

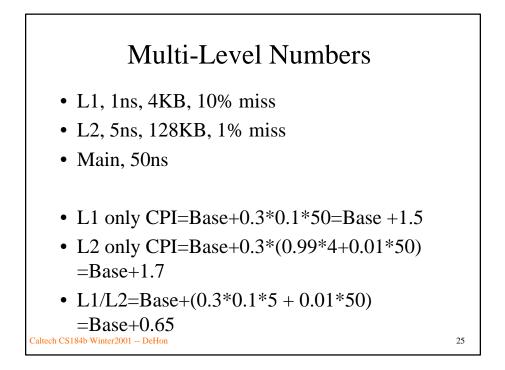

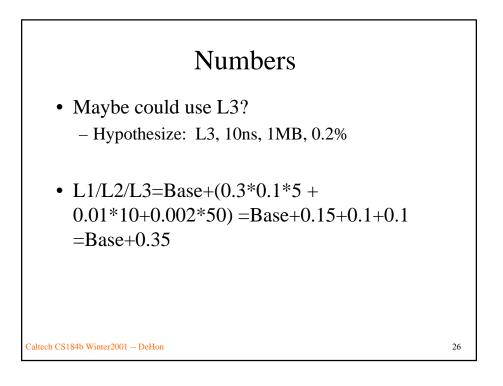

- multi-level caching

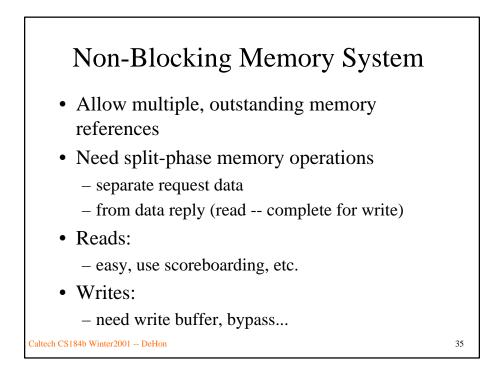

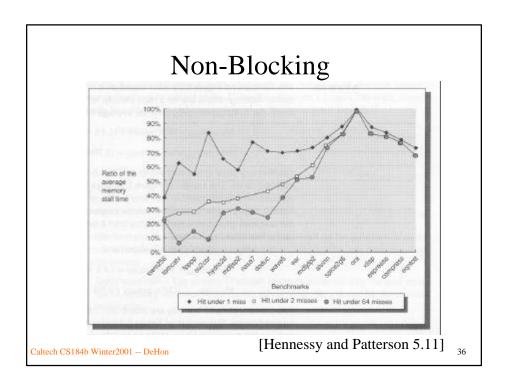

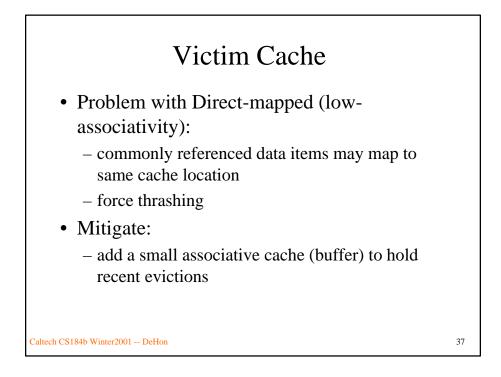

- split, nonblocking, victim

- prefetch

- coding/compiling for

Caltech CS184b Winter2001 -- DeHon

3

## Main Memory

- Past:

- DRAMs only provided a few output bits

- Wide memories by using multiple DRAM components in parallel (e.g. SIMMs)

- Larger deeper memories with multiple DRAM components on memory bus

- adds delay sharing bus, chip crossing to RAM

- time to select which component

- Memory access time slower than raw DRAM time

9

### Rate Note

- Previous slides:

- "L2 miss rate" = miss of L2

- all access; not just ones which miss L1

- If talk about miss rate wrt only L2 accesses

- higher since filter out locality from L1

- H&P: global miss rate

- Local miss rate: misses from accesses seen in L2

27

- Global miss rate

- Caltech CS184b White  $1_{20}$  miss rate × L2 local miss rate

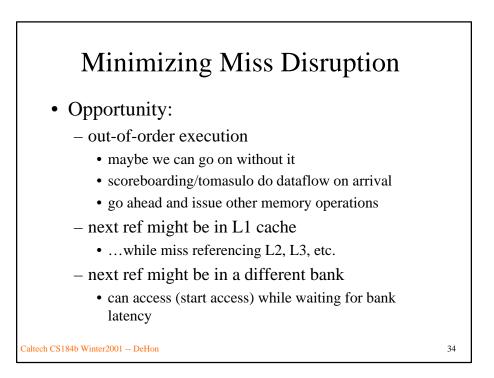

#### How disruptive is a Miss?

- With

- multiple issue

- a reference every 3-4 instructions

- memory references 1+ times per cycle

- Miss means multiple (4,8,50?) cycles to service

- Each miss could holds up 10's to 100's of instructions...

33

### Freedom

• Data layout

- place data referenced together close together

- same page

- same cache line

- common case code together

- bin to cache line by usage

- even if structure large, commonly accessed data in minimum number of cache lines

45

### Freedom

- Code layout

- pack together common case (main trace)

- close together

- packed appropriately into cache lines

- on same page

- off trace code may go further away

- make sure addresses in common traces **not** alias to same cache slot

47

• compiler use feedback from program run

# Big Ideas

- Structure

- spatial locality

- Engineering

- worked once, try it again...until won't work

- Exploit freedom which exists in application

- to favor what can do efficiently/cheaply

Caltech CS184b Winter2001 -- DeHon

49