## CS184b: Computer Architecture (Abstractions and Optimizations)

Day 13: May 4, 2003 Message Passing

Caltech CS184 Spring2003 -- DeHon

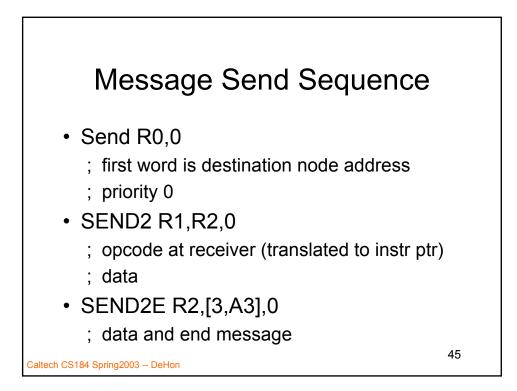

## Sample code: Combining Tree

COMBINE:

- MOVE [1,A3],COMB

- MOVE [2,A3], R1

- ADD R1,COMB.v,R1

- MOVE R1,COMB.v

- MOVE COMB.cnt,R2

- ADD R2,-1,R2

- MOVE R2,COMB.cnt

- BNZ R2, DONE

Caltech CS184 Spring2003 -- DeHon

- MOVE HEADER,R0

- SEND2 COMB.pnode,R0

- SEND2E COMB.paddr,R1 DONE:

- suspend

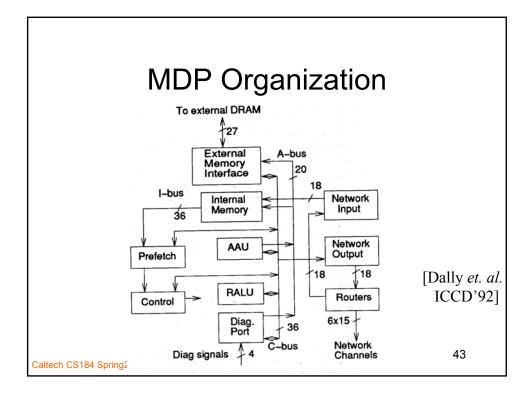

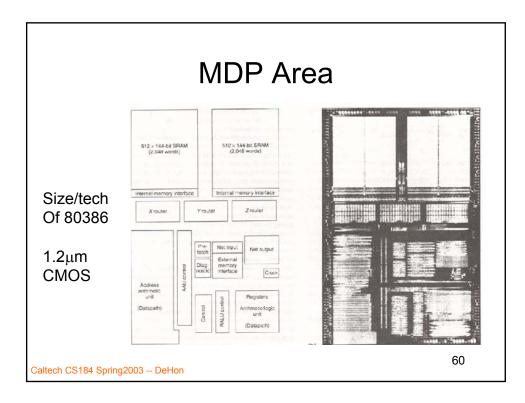

| MDP Area  |      |                               |                                  |                      |                                    |

|-----------|------|-------------------------------|----------------------------------|----------------------|------------------------------------|

|           | ~50% | Table 2. Chip area breakdown. |                                  |                      |                                    |

| ,         |      | Module                        | Dimensions<br>(mm)               | Area<br>(mm²)        | Transistors<br>(×10 <sup>3</sup> ) |

| Processor | ~33% | AAU                           | 3.7 × 7.0                        | 25.9                 | 75.0                               |

|           |      | RALU                          | 3.7 × 2.9                        | 10.7                 | 39.0                               |

| Vet 🦯     | ~10% | Diagnostic                    | 0.9 × 1.1                        | 1.0                  | 3.7                                |

|           |      | Prefetch                      | 0.9 × 1.1                        | 1.0                  | 3.2                                |

|           |      | Control<br>Internal memo      | 1.1 × 2.6<br>ory                 | 2.9                  | 8.7                                |

|           |      | interface<br>External memo    | 7.8 × 0.5                        | 3.9                  | 13.0                               |

|           |      | interface                     | 1.6 × 1.8                        | 2.9                  | 9.0                                |

|           |      | Net input                     | 1.8 × 0.7                        | 1.3                  | 4.4                                |

|           |      | Net output                    | 2.1 × 1.8                        | 3.8                  | 18.0                               |

|           |      | Routers                       | 8.4 × 1.3                        | 10.9                 | 29.0                               |

|           |      | RAM                           | 8.8 × 4.9                        | 43.1                 | 880.0                              |

|           |      | Clock                         | 0.7 × 0.8                        | 0.6                  | 0.1                                |

|           |      | Pads<br>Full chip             | <u>50.5 × 0.2</u><br>10.2 × 15.0 | <u>8.4</u><br>153.0* | <u>2.6</u><br>1,087.0              |