## CS184c: Computer Architecture [Parallel and Multithreaded]

Day 15: May 29, 2001 Interconnect

CALTECH cs184c Spring2001 -- DeHon

#### Previously

- CS184a: Day 11--14

- interconnect needs and requirements

- basic topology

- This quarter

- most systems require

- interfacing issues

- model, hardware, software

#### Today

- Issues

- Topology/locality/scaling

- (some review)

- Styles

- from static

- to online, packet, wormhole

- Online routing

CALTECH cs184c Spring2001 -- DeHon

#### Issues

- Bandwidth

- aggregate, per endpoint

- local contention and hotspots

- Latency

- Cost (scaling)

- locality

- Arbitration

- conflict resolution

- deadlock

- Routing

- (quality vs. complexity)

- Ordering

#### Topology and Locality

(Partially) Review

CALTECH cs184c Spring2001 -- DeHon

#### Simple Topologies: Bus

- Single Bus

- simple, cheap

- low bandwidth

- not scale with PEs

- typically online arbitration

- can be offline scheduled

#### **Bus Routing**

- Offline:

- divide time into N slots

- assign positions to various communications

- run modulo N w/ each consumer/producer

send/receiving on

time slot

- e.g.

- 1: A->B

- 2: C->D

- 3: A->C

- 4: A->B

- 5: C->B

- 6: D->A

- 7: D->B

- 8: A->D

CALTECH cs184c Spring2001 -- DeHon

#### **Bus Routing**

- Online:

- request bus

- wait for acknowledge

- Priority based:

- give to highest priority which requests

- consider ordering

- Got<sub>i</sub> = Want<sub>i</sub> ^ Avail<sub>i</sub> Avail<sub>i+1</sub>=Avail<sub>i</sub> ^ /Want<sub>i</sub>

- /Want; CALTECH cs184c Spring2001 -- DeHon

- Solve arbitration in log time using parallel prefix

- For fairness

- start priority at different node

- use cyclic parallel prefix

- deal with variable starting point

#### **Token Ring**

- On bus

- delay of cycle goes as N

- can't avoid, even if talking to nearest neighbor

- Token ring

- pipeline bus data transit (ring)

- high frequency

- can exit early if local

- use token to arbitrate use of bus

CALTECH cs184c Spring2001 -- DeHon

#### Multiple Busses

- Simple way to increase bandwidth

- use more than one bus

- Can be static or dynamic assignment to busses

- static

- A->B always uses bus 0

- C-> always uses bus 1

- dynamic

- arbitrate for a bus, like instruction dispatch to k

CALTECH cs184c Sprij<mark>identical</mark> €CPU resources

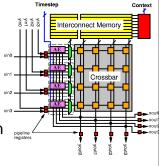

#### Crossbar

- No bandwidth reduction

- (except receiver at endoint)

- Easy routing (on or offline)

- Scales poorly

- N<sup>2</sup> area and delay

- No locality

CALTECH cs184c Spring2001 -- DeHon

#### Hypercube

- Arrange 2<sup>n</sup> nodes in n-dimensional cube

- At most n hops from source to sink

- High bisection bandwidth

- good for traffic

- bad for cost [O(n<sup>2</sup>)]

- May not be able to use all of bisect ?!?

- Exploit locality

- Node size grows as log(N)...or maybe log<sup>2</sup>(N)

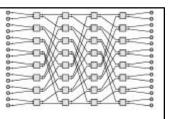

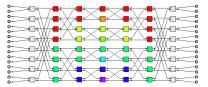

#### Multistage

- Unroll hypercube vertices so log(N), constant size switches per hypercube node

- solve node growth problem

- lose locality

- similar good/bad points for rest

CALTECH cs184c Spring2001 -- DeHon

## Hypercube/Multistage Blocking

- Minimum length multistage

- many patterns cause bottlenecks

## Hypercube/Multistage Blocking

- Solvable with non-minimum length (e.g. Beneš)

- Also solvable by routing multiple times through net

- I.e. Beneš is two back-to-back MINs

CALTECH cs184c Spring2001 -- DeHon

#

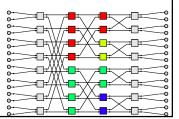

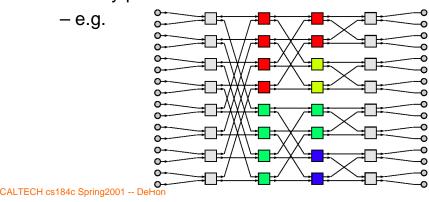

#### Beneš Routing

- Solve recursively by looping

- Start at a route

- Pick top or bottom half to route path

- Allocate at destination

- Look at other route must come in here

- Must take alternate path

- Continue until

- cycle closes or ends

CALTECH cs184c Spring2001 -- DeHon

- If unrouted at this level,

- pick new starting point and continue

- Once finish this level,

- repeat/recurse on top and bottom subproblems remaining

#### Online Hypercube Blocking

- If routing offline, can calculate Beneslike route

- Online, don't have time, global view

- Observation: only a few, canonically bad patterns

- Solution: Route to random intermediate

- then route from there to destination.

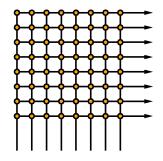

#### K-ary N-cube

- Alternate reduction from hypercube

- restrict to N<log(N) dimensional structure

- allow more than 2 ordinates in each dimension

- E.g. mesh (2-cube), 3D-mesh (3-cube)

- Matches with physical world structure

- Bounds degree at node

- Has Locality

- Even more bottleneck potentials

CALTECH 051840 make Channels wider (CS184a)

#### **Torus**

- Wrap around n-cube ends<sup>©</sup>

- -2-cube  $\rightarrow$  cylinder

- 3-cube  $\rightarrow$  donut

- Cuts worst-case distances

- Can be laid-out reasonable efficiently

- maybe 2x cost in channel width?

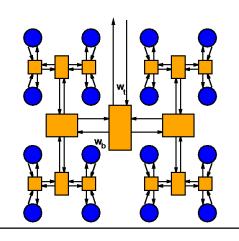

#### Fat-Tree

- Saw that communications typically has locality (CS184a)

- Modeled recursive bisection/Rent's Rule

- Leiserson showed Fat-Tree was (area, volume) universal

- w/in log(N) the area of **any** other structure

- exploit physical space limitations wiring in {2,3}-dimensions

CALTECH cs184c Spring2001 -- DeHon

#### **Universal Fat-Tree**

- P=0.5 for area universal

- P=2/3 for volume

- I.e. go as ratio

- surface/perimeter

- area/volume

- Directly related

- results on depop.

- CS184a day 13

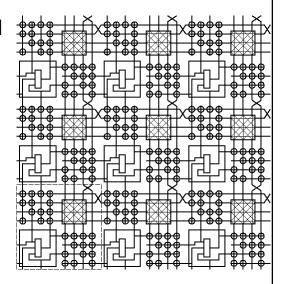

## Express Cube (Mesh with Bypass)

- Large machine in 2 or 3 D mesh

- routes must go through square/cube root switches

- vs. log(N) in fat-tree, hypercube, MIN

- Saw practically can go further than one hop on wire...

- Add long-wire bypass paths

CALTECH cs184c Spring2001 -- DeHon

#### CS184a Day 14

#### Segmentation

- To improve speed (decrease delay)

- Allow wires to bypass switchboxes

- Maybe save switches?

- Certainly cost more wire tracks

#### Routing Styles

CALTECH cs184c Spring2001 -- DeHon

#### Hardwired

- Direct, fixed wire between two points

- E.g. Conventional gate-array, std. cell

- Efficient when:

- know communication a priori

- fixed or limited function systems

- high load of fixed communication

- often control in general-purpose systems

- links carry high throughput traffic continually between fixed points

#### Configurable

- Offline, lock down persistent route.

- E.g. FPGAs

- Efficient when:

- link carries high throughput traffic

- (loaded usefully near capacity)

- traffic patterns change

- on timescale >> data transmission

CALTECH cs184c Spring2001 -- DeHon

#### Time-Switched

- Statically scheduled, wire/switch sharing

- E.g. TDMA, NuMesh, TSFPGA

- Efficient when:

- thruput per channel < thruput capacity of wires and switches

- traffic patterns change

- on timescale >> data transmission

#### Self-Route, Circuit-Switched

- Dynamic arbitration/allocation, lock down routes

- E.g. METRO/RN1

- Efficient when:

- instantaneous communication bandwidth is high (consume channel)

- lifetime of comm. > delay through network

- communication pattern unpredictable

- rapid connection setup important

CALTECH cs184c Spring2001 -- DeHon

#### Self-Route, Store-and-Forward, Packet Switched

- Dynamic arbitration, packetized data

- Get entire packet before sending to next node

- E.g. nCube, early Internet routers

- Efficient when:

- lifetime of comm < delay through net</p>

- -communication pattern unpredictable

- can provide buffer/consumption guarantees

- -packets small

### Self-Route, Wormhole Packet-Switched

- Dynamic arbitration, packetized data

- E.g. Caltech MRC, Modern Internet Routers

- Efficient when:

- lifetime of comm < delay through net</p>

- -communication pattern unpredictable

- can provide buffer/consumption guarantees

- message > buffer length

CALTECH cs184c Seriral 10 W Variable (? Long) sized messages

#### Online Routing

#### Costs: Area

- Area

- switch (1-1.5K / switch)

- larger with pipeline (4K) and rebuffer

- state (SRAM bit = 1.2K / bit)

- multiple in time-switched cases

- arbitrartion/decision making

- usually dominates above

- buffering (SRAM cell per buffer)

- can dominate

CALTECH cs184c Spring2001 -- DeHon

#### Costs: Latency

- Time local

- make decisions

- round-trip flow-control

- Time

- blocking in buffers

- quality of decision

- pick wrong path

- have stale data

#### Intermediate

- For large # of predictable patterns

- switching memory may dominate allocation area

- area of routed case < time-switched</li>

- Get offline, global planning advantage

- by source routing

- source specifies offline determined route path

- offline plan avoids contention

CALTECH cs184c Spring2001 -- DeHon

#### Offline vs. Online

- If know patterns in advance

- offline cheaper

- no arbitration (area, time)

- no buffering

- use more global data

- -better results

- As becomes less predictable

- benefit to online routing

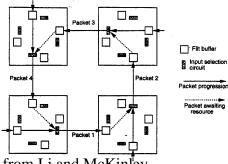

#### Deadlock

- Possible to introduce deadlock

- Consider wormhole routed mesh

[example from Li and McKinley,

CALTECH cs184c Spring2001 -- DeHPEEE Computer v26n2, 1993]

#### **Dimension Order Routing**

- Simple (early Caltech) solution

- order dimensions

- force complete routing in lower dimensions before route in next higher dimension

#### **Dimension Order Routing**

- Avoids cycles in channel graph

- Limits routing freedom

- Can cause artificial congestion

- consider

- (0,0) to (4,3)

- (1,0) to (4,2)

- (2,0) to (4,1)

- (3,0) to (4,0)

- [There is a rich literature on how to do better]

CALTECH cs184c Spring2001 -- DeHon

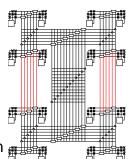

#### Virtual Channel

- Variation: each physical channel represents multiple logical channels

- each logical channel has own buffers

- blocking in one VC allows other VCs to use the physical link

#### Virtual Channel

- Benefits

- can be used to remove cycles

- e.g. separate increasing and decreasing channels

- · route increasing first, then decreasing

- · more freedom than dimension ordered

- prioritize traffic

- e.g. prevent control/OS traffic from being blocked by user traffic

- better utilization of physical routing channels

CALTECH cs184c Spring2001 -- DeHon

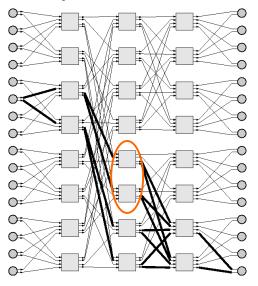

#### Lost Freedom?

- Online routes often make (must make) decisions based on local information

- Can make wrong decision

- I.e. two paths look equally good at one point in net

- but one leads to congestion/blocking further ahead

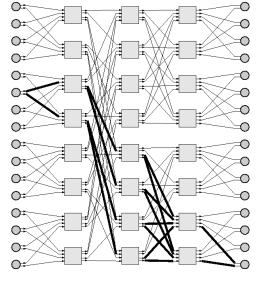

#### Multibutterfly Network

- Routers have multiple outputs in each logical direction

- Use to avoid congestion

- also faults

CALTECH cs184c Spring2001 -- DeHon

#### Multibutterfly Network

- Can get into local blocking when there is a path

- Costs of not having global information

#### Transit/Metro

- Self-routing circuit switched network

- When have choice

- select randomly

- · avoid bad structural cases

- When blocked

- drop connection

- allow to route again from source

- stochastic search explores all paths

- finds any available

CALTECH cs184c Spring2001 -- DeHon

#### **Chaos Router**

- For mesh/packet

- when blocked, allow route in any direction

- allows to take non-minimizing path to get around congestion

- avoids deadlock since blocking causes misroute

- Refs:

- [Konstantinidou and Snyder, SPAA90]

- http://www.cs.washington.edu/research/projects/lis/chaos/www/chaos.html

#### Big Ideas

- Must work with constraints of physical world

- only have 3 dimensions (2 on current VLSI) in which to build interconnect

- Interconnect can be dominate area, time

- gives rise to universal networks

- e.g. fat-tree

CALTECH cs184c Spring2001 -- DeHon

#### Big Ideas

- Structure

- exploit physical locality where possible

- Structure

- the more predictable behavior

- cheaper the solution

- exploit earlier binding time

- cheaper configured solutions

- allow higher quality offline solutions