# CS 179: GPU Computing

LECTURE 2: INTRO TO THE SIMD LIFESTYLE AND GPU INTERNALS

### Recap

Can use GPU to solve highly parallelizable problems

Looked at the a[] + b[] -> c[] example

CUDA is a straightforward extension to C++

- Separate CUDA code into .cu and .cuh files

- We compile with nvcc, NVIDIA's compiler for CUDA, to create object files (.o files)

Search for "Resource" links on <a href="http://courses.cms.caltech.edu/cs179/">http://courses.cms.caltech.edu/cs179/</a>

#### A Few GPU Keywords to Remember ...

- CUDA Nvidia's C++ like language for programming GPUs

- •nvcc nVidia CUDA compiler

- •SM -- Streaming Multiprocessor

- https://en.wikipedia.org/wiki/Stream processing

- •SIMD computation **Single instruction, multiple data (SIMD)** is a class of parallel computers in <u>Flynn's taxonomy</u>.

- https://en.wikipedia.org/wiki/SIMD

- •SIMT computation Single instruction, multiple threads

- <a href="https://en.wikipedia.org/wiki/Single">https://en.wikipedia.org/wiki/Single</a> instruction, multiple threads

# More GPU Keywords ...

- Threads A thread of execution is the smallest sequence of programmed instructions that can be managed independently by a <u>scheduler</u>, which is typically a part of the <u>operating system</u>

- https://en.wikipedia.org/wiki/Thread (computing)

- Blocks A thread block is a programming abstraction that represents a group of threads that can be executed serially or in parallel.

- https://en.wikipedia.org/wiki/Thread block (CUDA programming)

- Grids Nvidia GRID is a family of graphics processing units (GPUs)

- https://en.wikipedia.org/wiki/Nvidia GRID

- •Warps -- On the hardware side, a thread block is composed of 'warps'. A warp is a set of 32 threads within a thread block such that all the threads in a warp execute the same instruction. These threads are selected serially by the SM

- https://en.wikipedia.org/wiki/Thread\_block\_(CUDA\_programming)#Warps

- Warp Divergence All threads must generally execute the same code (if-then-else).

- https://cvw.cac.cornell.edu/gpu/thread\_div

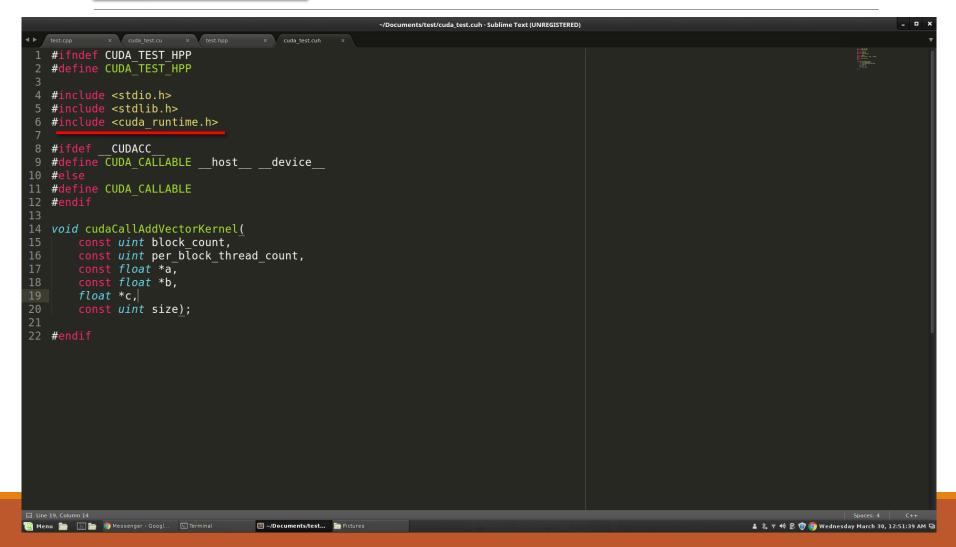

#### NVCC and G++

CUDA is simply an extension of other bits of code you write!!!!

- Evident in .cu/.cuh vs .cpp/.hpp distinction

- .cu/.cuh is compiled by nvcc to produce a .o file

- Since CUDA 7.0 / 9.0 there's support by NVCC for most C++11 / C++14 language features, but make sure to read restrictions for device code

- https://docs.nvidia.com/cuda/cuda-c-programming-guide/index.html#ccplusplus-language-support

- .cpp/.hpp is compiled by g++ and the .o file from the CUDA code is simply linked in using a "#include xxx.cuh" call

- No different from how you link in .o files from normal C++ code

```

~/Documents/test/cuda test.cu - Sublime Text (UNREGISTERED)

× test.hpp

× cuda test.cu

× cuda test.cuh

#include "cuda test.cuh"

global

void cudaAddVectorKernel(

const float *a,

const float *b,

float *c,

const uint size)

uint thread index = blockIdx.x * blockDim.x + threadIdx.x;

while (thread index < size) {</pre>

c[thread index] = a[thread index] + b[thread index];

thread index += blockDim.x * gridDim.x;

23 void cudaCallAddVectorKernel(

const uint block count,

const uint per block thread count,

const float *a,

const float *b,

28

float *c,

29

const uint size)

cudaAddVectorKernel<<<blook count, per block thread count>>>(a, b, c, size);

32 }

🔟 Menu 🛅 💹 🛅 🏮 Messenger - Googl... 🗵 Terminal

~/Documents/test...

Pictures

🛔 🔭 🕪 🕃 🛈 🧑 Wednesday March 30, 12:51:16 AM 🖳

```

```

~/Documents/test/test.cpp - Sublime Text (UNREGISTERED)

× cuda_test.cu × test.hpp

× cuda test.cuh

#include "test.hpp"

#include <stdio.h>

#include <iostream>

#include <stdlib.h>

6 #include <assert.h>

7 #include <cmath>

8 #include <cuda runtime.h>

#include "cuda test.cuh"

11

using namespace std;

12

int main(int argc, char **argv) {

14

const uint per block thread count = 1024;

const uint max block count = 65535;

17

const uint array size = 10000000;

float *a = new float[array size];

21

float *b = new float[array size];

float *c = new float[array size];

for (uint i = 0; i < array size; i++) {</pre>

a[i] = i;

b[i] = array size - i;

float *dev a;

float *dev b;

float *dev c;

Menu 🛅 💹 🛅 🏮 Edit cs179_2015_le... 🗵 Terminal

~/Documents/test...

Pictures

🛔 🖏 🕫 🐠 🖹 🕦 🧑 Wednesday March 30, 1:52:57 AM 🖳

```

```

~/Documents/test/test.cpp - Sublime Text (UNREGISTERED)

× cuda test.cu

× test.hpp

× cuda test.cuh

float *dev a;

float *dev b;

float *dev c;

cudaMalloc((void**) &dev a, array size * sizeof(float));

cudaMalloc((void**) &dev b, array size * sizeof(float));

cudaMalloc((void**) &dev c, array size * sizeof(float));

cudaMemcpy(dev a, a, array size * sizeof(float), cudaMemcpyHostToDevice);

cudaMemcpy(dev b, b, array size * sizeof(float), cudaMemcpyHostToDevice);

uint block count = min(max block count,

(uint) ceil(array size / (float) per block thread count));

cudaCallAddVectorKernel(

block count,

per block thread count,

dev a,

dev b,

dev c,

array size);

\operatorname{cudaMemcpy}(\overline{\mathsf{c}}, \operatorname{dev} \mathsf{c}, \operatorname{array} \operatorname{size} * \operatorname{sizeof}(float), \operatorname{cudaMemcpyDeviceToHost});

for (uint i = 0; i < array size; i++) {</pre>

assert(c[i] == array size);

delete[] a;

delete[] b;

delete[] c;

cudaFree(dev a);

cudaFree(dev b);

cudaFree(dev c);

~/Documents/test...

Pictures

Menu 🛅 💹 🛅 🌀 Edit cs179_2015_le... 💹 Terminal

🛓 💃 🕫 🐠 📵 📵 Wednesday March 30, 1:54:01 AM 🖳

```

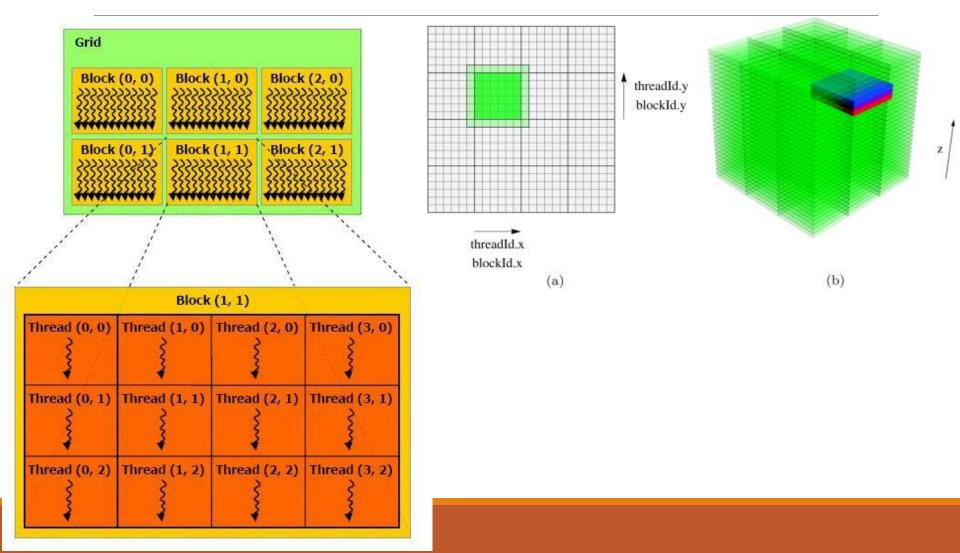

### Thread Block Organization

- Keywords you MUST know to code in CUDA:

- Thread Distributed by the CUDA runtime (threadIdx)

- Block A user defined group of 1 to ~512 threads (blockIdx)

- Grid A group of one or more blocks.

A grid is created for each CUDA kernel function called.

- Imagine thread organization as an array of thread indices

#### Block and Grid Dimensions

- For many parallelizeable problems involving arrays, it's useful to think of multidimensional arrays.

- E.g. linear algebra, physical modelling, etc, where we want to assign unique thread indices over a multidimensional object

- So, CUDA provides built in multidimensional thread indexing capabilities with a struct called dim3!

#### Dim3

dim3 is a struct (defined in vector\_types.h) to define your Grid and Block dimensions.

```

struct __device_builtin__ dim3

{

unsigned int x, y, z;

#if defined(__cplusplus)

__host__ _device__ dim3(unsigned int vx = 1, unsigned int vy = 1, unsigned int vz = 1) : x(vx), y(vy), z(vz) {}

__host__ _device__ dim3(uint3 v) : x(v.x), y(v.y), z(v.z) {}

__host__ _device__ operator uint3(void) { uint3 t; t.x = x; t.y = y; t.z = z; return t; }

#endif /* __cplusplus */

};

```

Works for dimensions 1, 2, and 3:

- dim3 grid(256); // defines a grid of 256 x 1 x 1 blocks

- dim3 block(512, 512); // defines a block of 512 x 512 x 1 threads

- foo<<<grid, block>>>(...);

# Grid/Block/Thread Visualized

# Single Instruction, Multiple Data (SIMD)

- SIMD describes a class of instructions which perform the same operation on multiple registers simultaneously.

- Example: Add some scalar to 3 registers, storing the output for each addition in those registers.

- Used to increase the brightness of a pixel

- CPUs also have SIMD instructions and are very important for applications that need to do a lot of number crunching

- Video codecs like x264/x265 make extensive use of SIMD instructions to speed up video encoding and decoding.

#### SIMD continued

- Converting an algorithm to use SIMD is usually called "Vectorizing"

- Not every algorithm can benefit from this or even be vectorized at all, e.x.

Parsing.

- Using SIMD instructions is not always beneficial though.

- Even using the SIMD hardware requires additional power, and thus waste heat.

- If the gains are small it probably isn't worth the additional complexity.

- Optimizing compilers like GCC and LLVM are still being trained to be able to vectorize code usefully, though there has been many exciting developments on this front in the last 2 years and is an active area of study.

- https://polly.llvm.org/

# SIMT (Single Instruction, Multiple Thread) Architecture

A looser extension of SIMD which is what CUDA's computational model uses

- Key differences:

- Single instruction, multiple register sets

- Wastes some registers, but mostly necessary for following two points

- Single instruction, multiple addresses (i.e. parallel memory access!)

- Memory access conflicts! Will discuss next week.

- Single instruction, multiple flow paths (i.e. if statements are allowed!!!)

- Introduces slowdowns, called 'warp-divergence.'

#### Good description of differences

- https://yosefk.com/blog/simd-simt-smt-parallelism-in-nvidia-gpus.html

- https://docs.nvidia.com/cuda/cuda-c-programmingguide/index.html#hardware-implementation

# Thread blocks and Warps – Questions?

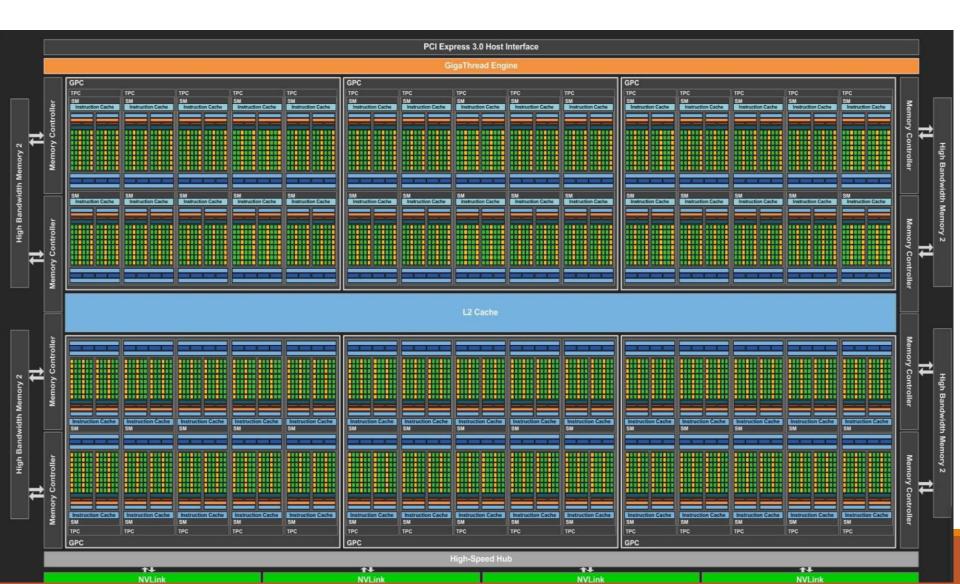

# Important CUDA Hardware Keywords!

- Streaming Multiprocessor (SM) Each contains (usually) 128 single precision CUDA cores (which execute a thread) and their associated cache.

- This is a standard based on your machines Compute Capability.

- Warp A unit of up to 32 threads (all within the same block)

- Each SM creates and manages multiple warps via the block abstraction. Assigns to each warp a Warp Scheduler to schedule the execution of instructions in each warp.

- Warp Divergence A condition where threads within a warp need to execute different instructions in order to continue executing their kernel.

- In order to maintain multiple flow path per instruction, threads in different 'execution branches' during an instruction are given no-ops.

- Causes threads to execute sequentially, in most cases ruining parallel performance.

- As of the Kepler (2012) architecture each Warp can have at most 2 branches, starting with Volta (2017) this condition has been nearly eliminated. For this class assume your code must only branch at most twice as we are not yet allocating Volta GPUs to this class.

- Inpendent Thread Scheduling fixes this problem by maintianing an execution state per thread. See Compute Capability 7.x

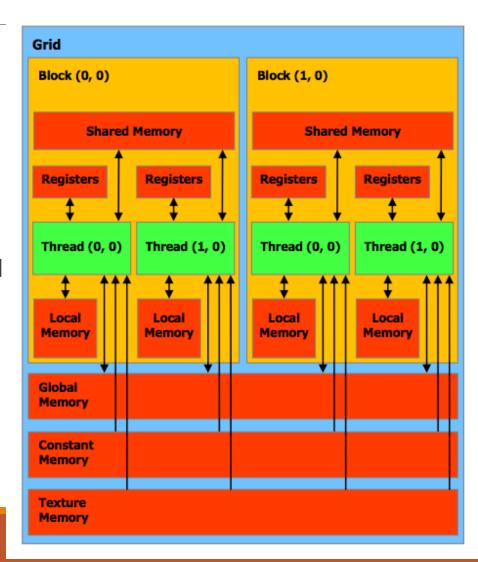

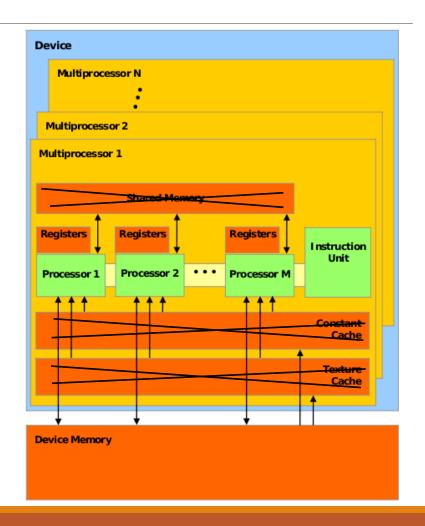

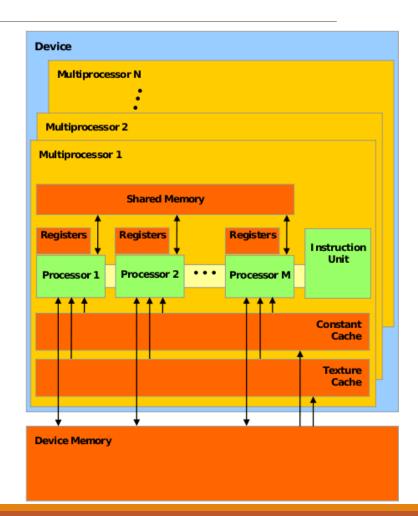

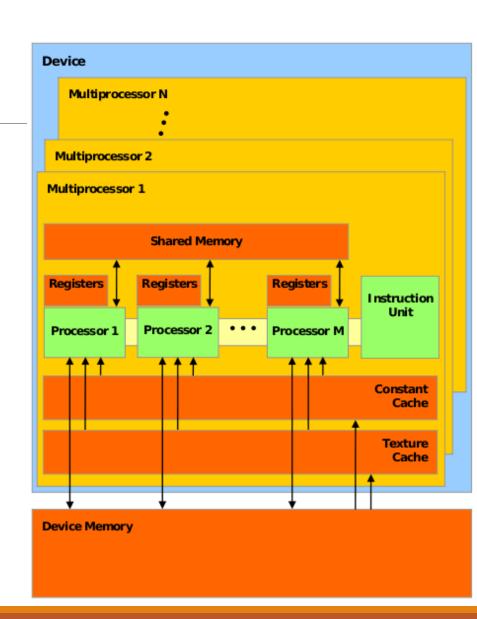

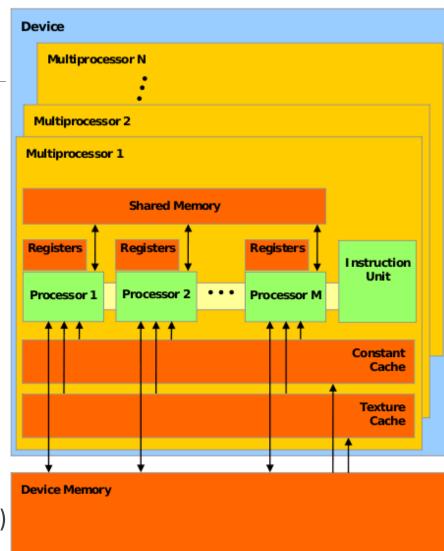

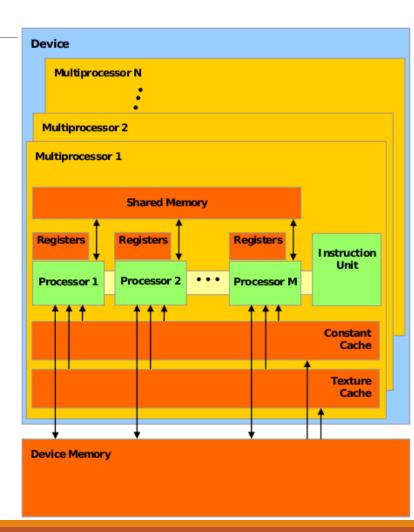

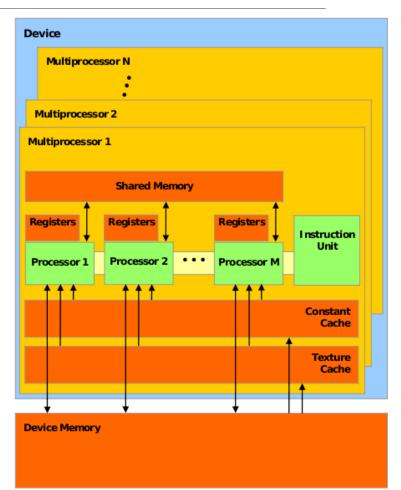

#### What a modern GPU looks like

The black Xs are just crossing out things you don't have to think about just yet. We'll cover memory next week

Think of **Device Memory** (we will also refer to it as **Global Memory**) as a RAM for your GPU

- Faster than getting memory from the actual RAM but still have other options

- Will come back to this in future lectures

#### GPUs have many **Streaming Multiprocessors** (SMs)

- Each SM has multiple processors but only one instruction unit (each thread shares program counter)

- Groups of processors must run the exact same set of instructions at any given time with in a single SM

When a kernel (the thing you define in .cu files) is called, the task is divided up into threads

Each thread handles a small portion of the given task

The threads are divided into a **Grid** of **Blocks**

- Both Grids and Blocks are 3 dimensional

- e.g.

```

dim3 dimBlock(8, 8, 8);

dim3 dimGrid(100, 100, 1);

Kernel<<<dimGrid, dimBlock>>>(...);

```

- However, we'll often only work with 1 dimensional grids and blocks

- e.g. Kernel<<<block\_count, block\_size>>>(...);

Maximum number of threads per block count is usually 512 or 1024 depending on the machine

Maximum number of blocks per grid is usually 65535

- If you go over either of these numbers your GPU will just give up or output garbage data

- Much of GPU programming is dealing with this kind of hardware limitations! Get used to it

- This limitation also means that your Kernel must compensate for the fact that you may not have enough threads to individually allocate to your data points

- Will show how to do this later (this lecture)

Each block is assigned to an SM

Inside the SM, the block is divided into **Warps** of threads

- Warps consist of 32 threads

- CUDA defined constant in cuda\_runtime.h

- All 32 threads MUST run the exact same set of instructions at the same time

- Due to the fact that there is only one instruction unit

- Warps are run concurrently in an SM

- If your Kernel tries to have threads do different things in a single warp (using if statements for example), the two tasks will be run sequentially

- Called Warp Divergence (NOT GOOD)

# Inside a GPU (fun hardware info)

In Fermi Architecture (i.e. GPUs with Compute Capability 2.x), each SM has 32 cores, later architectures have more.

- e.g. GTX 400, 500 series

- 32 cores is not what makes each warp have 32 threads. Previous architecture also had 32 threads per warp but had less than 32 cores per SM

- Some early Pascal (2016) GPUs (GP100) had 64 cores per SM, but later chips in that generation (GP104) had 128 core model.

- Turing (2018) maintains 128 core standard

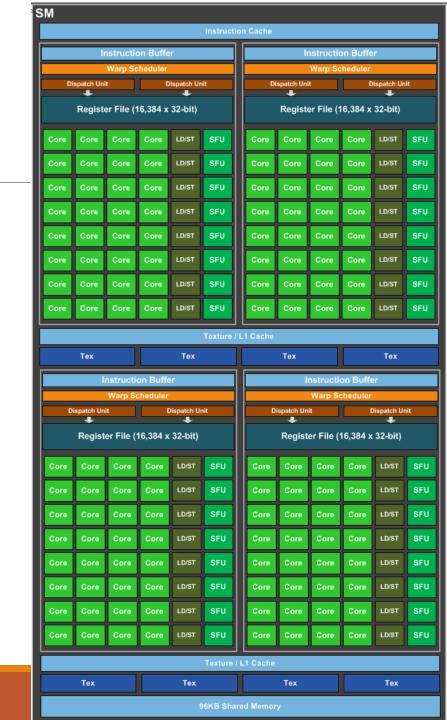

# Streaming Multiprocessor

- Shown here is a Pascal GP104 GPU

Streaming Multiprocessor that can be found in a GTX1080 graphics card.

- The exact amount of Cache and Shared Memory differ between GPU models, and even more so between different architectures.

- Whitepapers with exact information can be gotten from Nvidia (use Google)

- https://international.download.nvidia.com/geforcecom/international/pdfs/GeForce\_GTX\_1080\_Whitepaper\_FINA L.pdf

- http://www.nvidia.com/content/PDF/productspecifications/GeForce GTX 680 Whitepaper FINAL.pdf

- "nvidia kepler whitepaper"

# A[] + B[] -> C[] (again)

```

~/Documents/test/test.cpp - Sublime Text (UNREGISTERED)

× cuda test.cu × test.hpp

× cuda test.cuh

#include "test.hpp"

#include <stdio.h>

#include <iostream>

#include <stdlib.h>

6 #include <assert.h>

7 #include <cmath>

8 #include <cuda runtime.h>

9 #include "cuda test.cuh"

11 using namespace std;

12

13 int main(int argc, char **argv) {

14

const uint per block thread count = 1024;

const uint max block count = 65535;

const uint array size = 10000000;

float *a = new float[array size];

float *b = new float[array size];

float *c = new float[array size];

for (uint i = 0; i < array size; i++) {</pre>

a[i] = i;

b[i] = array size - i;

float *dev a;

float *dev b;

float *dev c;

Menu 🛅 💹 🛅 🏮 Edit cs179_2015_le... 🗵 Terminal

~/Documents/test...

Pictures

🛔 🖏 🕫 🐠 🖹 🕦 🧑 Wednesday March 30, 1:52:57 AM 🖳

```

# A[] + B[] -> <u>C[] (again</u>)

```

~/Documents/test/test.cpp - Sublime Text (UNREGISTERED)

x cuda_test.cuh

× cuda test.cu

x test.hpp

float *dev a;

float *dev b;

float *dev c;

cudaMalloc((void**) &dev a, array size * sizeof(float));

cudaMalloc((void**) &dev b, array size * sizeof(float));

cudaMalloc((void**) &dev c, array size * sizeof(float));

cudaMemcpy(dev a, a, array size * sizeof(float), cudaMemcpyHostToDevice);

cudaMemcpy(dev b, b, array size * sizeof(float), cudaMemcpyHostToDevice);

uint block count = min(max block count,

(uint) ceil(array size / (float) per block thread count));

cudaCallAddVectorKernel(

block count,

per block thread count,

dev a,

dev b,

dev c,

array size);

\operatorname{cudaMemcpy}(\overline{\mathsf{c}}, \operatorname{dev} \mathsf{c}, \operatorname{array} \operatorname{size} * \operatorname{sizeof}(float), \operatorname{cudaMemcpyDeviceToHost});

for (uint i = 0; i < array size; i++) {</pre>

assert(c[i] == array size);

delete[] a;

delete[] b;

delete[] c;

cudaFree(dev a);

cudaFree(dev b);

cudaFree(dev c);

Menu 🛅 💹 🛅 🌀 Edit cs179_2015_le... 💹 Terminal

~/Documents/test...

Pictures

🛓 💃 🕫 🐠 📵 📵 Wednesday March 30, 1:54:01 AM 🖳

```

# A[] + B[] -> C[] (new!!)

```

~/Documents/test/cuda test.cu - Sublime Text (UNREGISTERED)

× cuda test.cu

× test.hpp

× cuda test.cuh

#include "cuda test.cuh"

global

void cudaAddVectorKernel(

const float *a,

const float *b,

float *c,

const uint size)

uint thread index = blockIdx.x * blockDim.x + threadIdx.x;

while (thread index < size) {</pre>

/st add a and b into c st/

c[thread index] = a[thread index] + b[thread index];

thread index += blockDim.x * gridDim.x;

23 void cudaCallAddVectorKernel(

const uint block count,

const uint per block thread count,

const float *a,

const float *b,

28

float *c,

const uint size)

cudaAddVectorKernel<<<blook count, per block thread count>>>(a, b, c, size);

32 }

u Menu 🛅 💹 🛅 🏮 Messenger - Googl... 🗵 Terminal

~/Documents/test...

Pictures

🛕 🛼 🕫 🕪 📳 🚺 🧑 Wednesday March 30, 12:51:16 AM 🖳

```

# Questions for hardware?

#### Stuff that will be useful later

```

~/Documents/test/cuda test.cuh - Sublime Text (UNREGISTERED)

× cuda test.cu × test.hpp

#ifndef CUDA TEST HPP

#define CUDA TEST HPP

#include <stdio.h>

#include <stdlib.h>

6 #include <cuda runtime.h>

8 #ifdef CUDACC

#define CUDA CALLABLE host device

#define CUDA CALLABLE

void cudaCallAddVectorKernel(

const uint block count,

const uint per block thread count,

const float *a,

const float *b,

float *c,

const uint size);

22 #endif

u Menu 🛅 💹 🛅 🏮 Messenger - Googl... 🗵 Terminal

~/Documents/test...

Pictures

🛔 🔭 🕪 📵 🕡 🧑 Wednesday March 30, 12:51:39 AM 🖳

```

#### Stuff that will be useful later

```

~/Documents/repos/cs81/src/swarm.cuh - Sublime Text (UNREGISTERED)

× cuda_test.cu

× test.hpp

× cuda test.cuh

#ifndef SWARM CUH

#define SWARM CUH

#include <cstdio>

#include <cuda runtime.h>

#include "constants.hpp"

#include "utils.hpp"

struct GPUVec3d {

double x;

double v:

double z;

CUDA CALLABLE GPUVec3d():

CUDA CALLABLE GPUVec3d(double x, double y, double z);

CUDA CALLABLE GPUVec3d(const GPUVec3d &v);

CUDA CALLABLE ~GPUVec3d();

CUDA CALLABLE double sqNorm();

CUDA CALLABLE const GPUVec3d & operator = (const GPUVec3d& rhs);

CUDA CALLABLE bool operator == (const GPUVec3d& rhs) const;

CUDA CALLABLE bool operator!=(const GPUVec3d& rhs) const;

CUDA_CALLABLE const GPUVec3d &operator+=(const GPUVec3d &rhs);

CUDA_CALLABLE const GPUVec3d &operator-=(const GPUVec3d &rhs);

CUDA_CALLABLE const GPUVec3d & operator*=(const double d);

CUDA CALLABLE const GPUVec3d & operator /= (const double d);

CUDA CALLABLE friend const GPUVec3d operator+(const GPUVec3d &lhs,

GPUVec3d &rhs):

CUDA CALLABLE friend const GPUVec3d operator-(const GPUVec3d &lhs,

const GPUVec3d &rhs);

CUDA CALLABLE friend const GPUVec3d operator*(const GPUVec3d &lhs,

const double d);

CUDA CALLABLE friend const GPUVec3d operator*(const double d,

const GPUVec3d &rhs):

CUDA CALLABLE friend const GPUVec3d operator/(const GPUVec3d &lhs,

const double d):

41 class SwarmParticle;

Menu 🛅 🔟 🛅 🏮 Edit cs179_2015_le... 🖺 ~/Documents/rep... 🛅 Pictures

🛓 🔭 🕬 📵 🕡 🧑 Wednesday March 30, 4:11:19 AM 🖳

```

#### Stuff that will be useful later

```

~/Documents/test/cuda_test.cu - Sublime Text (UNREGISTERED)

× cuda test.cu

× cuda test.cuh

#include "cuda test.cuh"

global

4 void cudaAddVectorKernel(

const float *a,

const float *b,

float *c,

const uint size)

uint thread index = blockIdx.x * blockDim.x + threadIdx.x;

while (thread index < size) {</pre>

c[thread index] = a[thread index] + b[thread index];

thread index += blockDim.x * gridDim.x;

23 void cudaCallAddVectorKernel(

const uint block count,

const uint per block thread count,

const float *a,

const float *b,

28

float *c.

const uint size)

cudaAddVectorKernel<<<blook count, per block thread count>>>(a, b, c, size);

32 }

u Menu 🛅 💹 🛅 🏮 Messenger - Googl... 🗵 Terminal

~/Documents/test...

Pictures

🛕 🛼 🕫 🕪 📳 🚺 🧑 Wednesday March 30, 12:51:16 AM 🖳

```

#### Next Time...

Global Memory access is not that fast

- Tends to be the bottleneck in many GPU programs

- Especially true if done stupidly

- We'll look at what "stupidly" means

Optimize memory access by utilizing hardware specific memory access patterns

Optimize memory access by utilizing different caches that come with the GPU